Рубрики

МЕНЮ

Создана самая маленькая в мире ячейка памяти

Традиционно массив памяти SRAM в составе процессоров занимает приличную площадь (как правило, для кеш-памяти первых трёх уровней)

Виталий Войчук

Его сложно уменьшить, поскольку каждая ячейка SRAM содержит до шести транзисторов, сообщает "3Dnews".

Память SRAM должна быть максимально производительной и, поэтому, опирается на логику, а не на заряд в конденсаторе, как обычная память DRAM. Всё это создаёт проблемы с масштабированием ячейки SRAM при переходе на более мелкие технологические нормы производства. Новые техпроцессы всегда начинают испытывать с выпуска массивов SRAM. Если это получается, то затем переходят к опытному выпуску процессорной логики.

На сегодня самой маленькой ячейкой SRAM могла похвастаться Samsung. По этому параметру она обогнала компанию Intel. Samsung представила 6-транзисторную ячейку SRAM площадью 0,026 мкм. Для выпуска 256-Мбит массива опытной памяти был использован 7-нм техпроцесс Samsung 7LPP с частичным использованием EUV-сканеров. Через несколько месяцев этот техпроцесс будет запущен в коммерческих масштабах. Выпустить ячейку SRAM ещё меньшей площади сумели бельгийский центр разработок Imec и стартап Unisantis. Пусть вас не смущает упоминание стартапа. Главным технологом и директором компании Unisantis является изобретатель NAND-флеш Фудзио Масуока. Он даже получил за это награду европейского уровня Economist Awards.

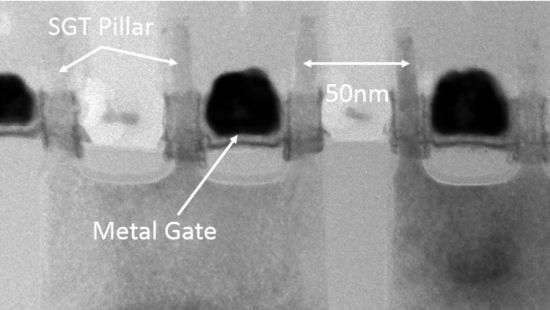

Unisantis и Imec создали 6-транзистрную структуру ячейки SRAM площадью не более 0,0205 мкм. Для этого разработчики отказались от горизонтальных транзисторных структур типа FinFET (вертикальные рёбра каналов, окружённые затворами с трёх сторон) и создали вертикальные транзисторные каналы в виде колонн, полностью окружённые затворами (SGT, Surrounding Gate Transistor). Это одна из разновидностей кольцевых или охватывающих затворов GAA (Gate-All-Around). Samsung начнёт использовать подобные затворы в 2021 году при переходе на 3-нм техпроцесс.

Центр Imec и Unisantis разработали технологию SGT для выпуска SRAM с техпроцессом 5 нм. Партнёры предлагают начать уплотнять SRAM уже через год или два.

Переход с горизонтальных структур на вертикальные колонны транзисторных каналов позволит снизить площадь массивов SRAM на 20-30 %. Продемонстрированный образец, например, показал уменьшение площади массива на 24 %. Если для выпуска "колонновидной" SRAM использовать EUV-литографию, то за счёт снижения циклов обработки пластин стоимость производства вертикальных каналов окажется такой же, как и каналов FinFET. Вертикальные каналы SGT обеспечат меньшие токовые утечки и лучшую стабильность параметров транзисторов, а также устранят проблему дальнейшего снижения масштаба. Единственным недостатком SGT структур может считаться их недостаточная производительность для использования в логических элементах (по токовым характеристикам SGT примерно втрое хуже FinFET). Но это не мешает SGT структурам идеально подходить для производства DRAM, SRAM и NAND.

Фото: Imec

Читайте Comments.ua в Google News

Новости партнеров